19.2. 功能特性¶

19.2.1. 主要特性¶

支持单线 SPI 接口

可编程的时钟极性和相位

AHB 总线接口,数据总线位宽 32 位,支持配置 8 / 32 bit 数据位宽传输

TX FIFO 深度为 16×32bit ,RX FIFO 深度为 8×32bit

支持主机模式和从机模式

作为主机 (master) 时,支持最多1个 cs 控制接口,可用于控制一个 slave

支持 DMA 控制器接口,使用握手接口实现传输请求,通过总线与 DMA 控制器连接

主机模式下,接收到的串行数据位 (RXD) 的采样时间延时可编程,从而实现更高的串行数据比特率

从机模式下,从机只接收数据时,支持无 cs 信号模式,cs 信号可由内部软件控制一直拉低

19.2.2. 功能描述¶

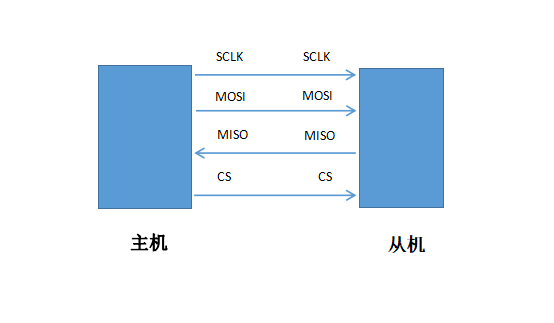

19.2.2.1. SPI 引脚连接如下:¶

SPI (Standard-SPI) 采用 4 个引脚与外部器件相连:

MISO:主设备输入/从设备输出引脚。该引脚在从模式下发送数据,在主模式下接收数据。

MOSI:主设备输出/从设备输入引脚。该引脚在主模式下发送数据,在从模式下接收数据。

CLK:串口时钟,作为主设备的输出,从设备的输入。

CS:从设备选择。这是一个可选的引脚,用来选择主/从设备。它的功能是用来作为“片选引脚”,让主设备可以单独地与特定从设备通讯,避免数据线上的冲突。

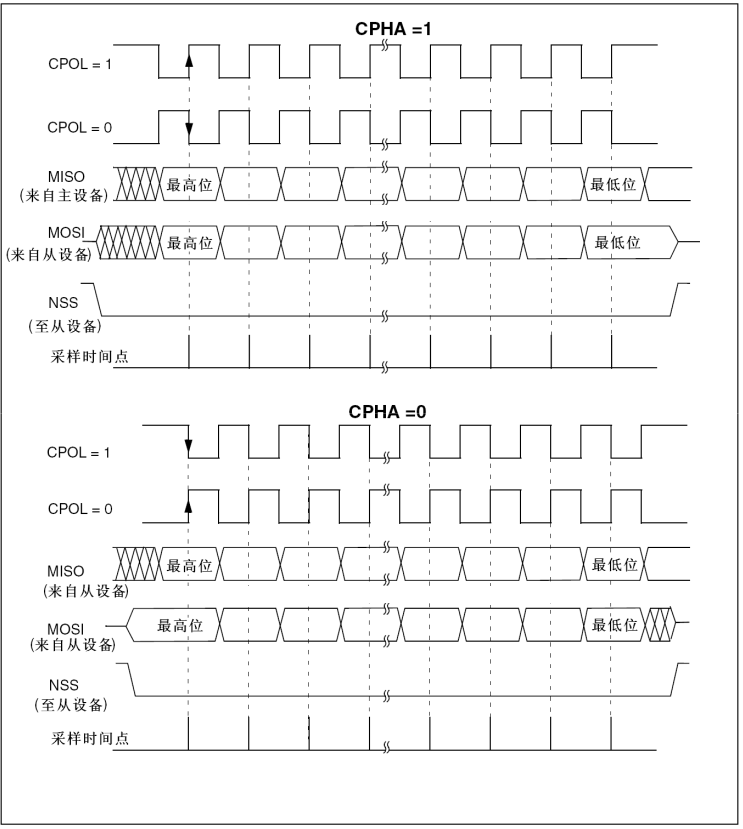

19.2.2.2. 时钟信号的相位和极性¶

主机可以配置与数据有关的时钟极性和相位。Motorola 将这两个选项分别命名为 CPOL 和 CPHA (用于时钟极性和相位),时序图如上所示:

CPOL 确定时钟的极性:

CPOL = 0 时,SCK 引脚在空闲状态保持低电平

CPOL = 1 时,SCK 引脚在空闲状态保持高电平

CPHA 确定时钟的采样边沿:

CPHA = 0 时,SCK 时钟的第一个边沿进行数据位采样,数据在第一个时钟边沿被锁存

CPHA = 1 时,SCK 时钟的第二个边沿进行数据位采样,数据在第二个时钟边沿被锁存